# A REVIEW ON DESIGNING SUB THRESHOLD FLIP FLOPS FOR WIRELESS SENSOR NETWORK

Neetu Kumari, Nikita Patel, Satyajit Anand and Partha Pratim Bhattacharya

## ABSTRACT

In a sensor node, maximum power is consumed by microcontroller since most of the functionalities are controlled or performed by it. Flip flop occupies major portion of microcontroller. Hence designing a low powerflip flop cell is highly important forprolonging the life time of network. In this paper, we have reviewed and critically analyzed different sub threshold flip flop cells for wireless sensor networks.

**Keywords:** Microcontroller, wireless sensor network, network lifetime, dynamic power management, dynamicpower dissipation, static power dissipation and D flip flops.

**Reference** to this paper should be made as follows: Neetu Kumari, Nikita Patel, Satyajit Anand and P.P, Bhattacharya (2019), "A Review on Designing Sub Threshold Flip Flops for Wireless Sensor Network" Int. J. Electronics Engineering and Applications, Vol. 7, No. 2, pp. 01-09

#### **Biographical notes:**

**Neetu Kumari** was born in India on November 5, 1988. She received her B.Tech degree in Electronics and Communication Engineering from RGPV, Bhopal, India in 2011 and currently is a M. Tech (VLSI) student in Mody Institute of Technology and Science (Deemed University), Rajasthan, India. Her research interest lies in Dynamic Power Management in Wireless Sensor Networks.

Satyajit Anand received the B.E. degree in Electronics and Communication Engineering from Anna University, Chennai, Tamilnadu, in 2007, M.Tech degree in VLSI Design from the MITS University, Lakshmangarh, Sikar, Rajasthan, in 2010 respectively. Currently, He is an Assistant Professor of Electronics and Communication Engineering at MITS University, Lakshmangarh. His teaching and research areas include Digital Signal Processing, Digital VLSI Design and Low Power VLSI Device Design. He has published over 25 papers in the field of VLSI. He also got a 2nd position in "An all India online technological innovation contest" which was conducted by JOHN DEERE IN 2011.

**Dr. Partha Pratim** Bhattacharya was born in India on January 3, 1971. He has 17 years of experience in teaching and research. He served many reputed educational Institutes in India in various positions. At present he is working as Professor in Department of Electronics and Communication Engineering in the Faculty of Engineering and Technology, Mody Institute of Technology and Science (Deemed University), Rajasthan, India. He worked on Microwave devices and systems and mobile cellular communication systems. He has published more than 100 papers in refereed journals and conferences. His present research interest includes mobile cellular communication, wireless sensor network and cognitive radio.

**Dr. Bhattacharya** is a member of The Institution of Electronics and Telecommunication Engineers, India and The Institution of Engineers, India. He is the recipient of Young Scientist Award from International Union of Radio Science in 2005. He is working as the editorial board member and reviewer in many reputed journals

Published by: International Associations of Professionals and Technical Teachers (IAPATT)

### I. INTRODUCTION

Wireless sensor network (WSN) consists of low cost, low power distributed devices which is called sensor nodes. The role of each sensor node is to sense physical and environmental changes such as temperature, pressure etc. Each node has a limited communication range and storage capability.

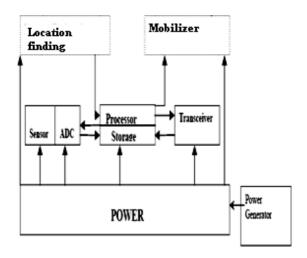

Wireless sensor network is made up of four components: sensing unit, processing unit, transmission unit and power unit [1] as shown in Figure 1.

- Sensing unit: Sensing unit consist of sensor and analog to digital converters (ADCs). Sensor convert physical phenomenon to electrical signals. The analog signals produced by sensor are converted to digital signals by ADC and then fed to processing unit.

- Processing unit: Processing unit consists of microprocessor or microcontroller. This part of the node helps to control task scheduling, to calculate energy, to define communication protocols, to make suitable coordination and for data manipulation and data transfer.

- Transmission unit: Transmission unit receives the information from the CPU and then transmit it to the outside world.

- Power unit: The power supply unit is a crucial component of wireless sensor network. Battery power is the main source of energy. It supplies power to the complete sensor node, and hence plays a vital role in determining sensor node lifetime

Wireless sensor network find wide range of applications such as radiation level control, battlefield, noise pollution control, biological detection, structural health monitoring etc [2]. All sensors in the wireless sensor networks are battery operated which has limited power supply. Once the sensor nodes are deployed it is not possible to replace battery in the nodes. Therefore, optimal energy consumption by the nodes is necessary. Dynamic power management is one of the techniques to reduce power consumption. It shuts down the sensor node when there is no work and wakes up when required [3]. This yields better savings of energy and enhance lifetime.

#### Applications of WSNs

Applications of wireless sensor network are in -

- Building monitoring and control: Sensors embedded in a building can reduce energy cost by monitoring the temperature and lighting conditions in the buildings. In a ventilation system, sensor can be used to detect biological agents or chemical pollutants.

- Health care monitoring: The medical applications can be of two types: wearable and implanted. In wearable application devices are used on the surface of a human body or just at close proximity of the user. The implantable medical devices are those that are inserted inside human body.

- Industrial Monitoring: Using smart sensors, the condition of equipments in field and factories can be monitored to alert for imminent failures. This reduces cost for service and maintenance, increase machine up-time, improve customer satisfaction and even save lives.

- Agriculture: Wireless sensor network allows precise monitoring of crops at the time of its growth so that farmer can immediately know the state of the item at all its stages which will ease the decision process regarding the time of harvest [4].

- Smart Home Monitoring: Wireless sensors embedded within everyday objects forming a wireless sensor network is used to monitor the activities performed in a smart home.

- Environmental Monitoring: Sensors can be used for: air quality monitoring, air pollution monitoring, forest fire detection, landslide detection, water quality monitoring and so on. Sensors can also monitor biological or chemical hazards to provide early warnings.

## **2. RELATED WORK**

Complementary Metal-Oxide-Semiconductor (CMOS) is the technology for designing integrated circuits that employ logic using both n- and p-channel MOSFET's. CMOS is the major technology utilized in manufacturing digital IC's and is now widely used in microprocessors, memories, and digital ASIC's. The low input currents required by a CMOS circuit results in lower power consumption, which is the major advantage of CMOS.

The total power dissipation of a circuit can be expressed as the sum of the static and the dynamic power dissipation component [5]. The dynamic power dissipation occurs due to charging and discharging of load capacitances and can be approximated as:

$Pdyn = 1/2 \cdot \alpha \cdot CL \cdot V \ DD2 \cdot f$

where,  $\alpha$  is the probability of a signal transition within a clock period, CL is the circuit capacitance to switch, VDD is the power supply voltage and f is the clock frequency.

From this equation, it can be observed that the dynamic power dissipation depends quadratically on the power supply voltage. Hence, reducing VDD is an effective way to reduce the dynamic power dissipation. Static power dissipation occurs due to non-ideal secondary CMOS effects such as subthreshold leakage current and other leakage currents in the transistor. Assuming a constant leakage current, the static power dissipation is given as [6]:

### Pstatic=Istatic·VDD

Subthreshold leakage current for Vgs < Vtn for an n-type MOS transistor is given by:

Ids= I0e(1- $\kappa$ )Vbs/Vt e $\kappa$ Vgs/Vt(1 - e-Vds/Vt + Vds/V0)

where,

Vgs is the gate-to-source voltage

Vds is the drain-tosource voltage

Vbs is the substrate-to-source voltage (known as the body effect)

I0 is the zero-bias current for the given device

Vt is the temperature voltage

Vt = kT/qV0 is the early voltage,  $\kappa$  is the effectiveness of the gate potential in controlling the channel current.

By reducing the supply voltage, and thus also Vgs, below the threshold voltage, the transistor channel is never fully inverted, but operates in weak or moderate inversion when the transistor is in 'on' state. For a n-type MOS transistor, weak inversion occurs when Vgs is approximately 100mV or more below the threshold voltage Vtn, and strong inversion occurs when Vgs is 100mV or more above Vtn. The region between weak and strong inversion is called moderate inversion

## **3. PROPOSED WORK**

Flip flop is a major kind of sequential logic which plays an important role in modern synchronous digital circuits. In this section, we have discussed different sub threshold flip flop cells for wireless sensor networks.

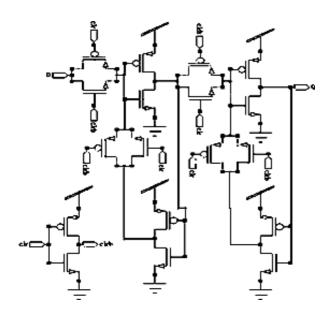

#### A. C2MOS D flip flop

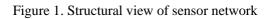

C2MOS stands for clocked CMOS and is an inverter-based master-slave D flip flop (DFF) which uses clocked inverters to control the loading of a new value, and to break the feedback loop. It is based on using two clocked inverter-based D-latches. The schematic for the C2MOS is shown in Figure 2.

In [7], this flip flop was proposed and simulated with a power supply voltage ranging from 350mV to 150mV at an operating frequency of 1MHz. The simulation result shows a delay time of 129.6ns and power dissipation of 350pW.So this

D flip flop cell was resized and modified [9] to reduce work voltage as shown in Figure 3. The VDDmin of improved C2MOS reduced from 230mV to 180mV.

A Review on Designing Sub Threshold Flip Flops for Wireless Sensor Network

Figure 2.C<sup>2</sup>MOS D flip flop

Figure 3.modified C<sup>2</sup>MOS D flip flop

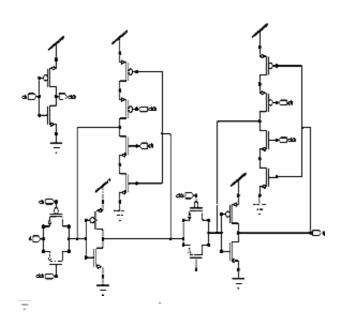

### B. Transmission-gate Master-Slave (TGMS) flip-flop

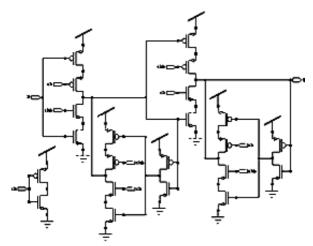

The TGMS flip-flop is composed of two transmission gate-based latches operating on complementary clocks. This flip flop may be sensitive to clock-skew of its two complementary clock- phases as shown in Figure 4.

This flip flop was proposed and simulation was carried out with power supply voltage ranging from 350mV to 150mV and operating frequency of 1 MHz [7]. The simulation result shows a delay time of 129.8ns and power dissipation of 332.7pW. Hence, it was resized and modified to reduce work voltage [9]. The VDDmin of improved TGMS reduced from 230mV to 190mV.

Figure 4. Transmission-gate Master-Slave (TGMS) flip-flop

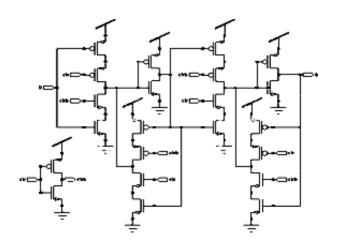

#### C. PowerPC 603

This flip-flop is a combination of the TGMS and C2MOS flip-flops, using clocked inverters instead of feedback transmission gates as shown in Figure 5. It was used in the PowerPC 603 microprocessor data-path. For driving a high load, the static PowerPC 603 flip-flop shows the best overall performance, with a delay time of 16 ns and a power dissipation of 666 pW at 250mV. If the flip-flop is driving a lower load, the dynamic TGMS cell offers less delay and power dissipation, providing 20% lower delay time i.e. 119.7ns and 30% lower power dissipation i.e. 284.9pW compared to the PowerPC 603 flip-flop at VDD 250mV.

This flip flop cell was resized and simulated in 65nm and 90nm technology to reduce delay time and power dissipation [8]. In general, flip-flops in the 65 nm process show a lower delay time at the cost of higher power consumption compared to the same flip-flop designs in the 90 nm process. For sub-threshold operations, the PowerPC 603 has an increase in the EDP (energy delay product) value of 10 times in the 90 nm process compared to the 65 nm process. PowerPC 603 are structured by logics of inverters. So the inverter was redesigned so strong that it is functional under a lower supply voltage [9].

Figure 5.PowerPC 603

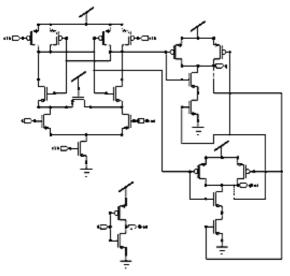

#### D. Sense Amplifier based D flip flop

The Sense-Amplifier based flip-flop (SAFF) consists of a sense-amplifier and S-R latch for capturing the output of the sense-amplifier as shown in Figure 6. With a power supply voltage ranging from 125mV to 1V this flip flop was simulated in 65nm and 90nm technology [8]. The simulation result shows a delay time of 19.6ns and power dissipation of 6.9nW in 65nm technology and delay time of 36.8ns and power dissipation of 1.5nW in 90nm technology. In [9] DFF cell was resized and modified to reduce work voltage.

Figure 6.Sense Amplifier based D flip flop (SAFF)

# CONCLUSION

In this paper, some widely used D flip flop cells are analyzed in sub threshold region. It is seen that PowerPC 603 flip flop cell offers best delay time and power dissipation of 120ns and 285pW respectively at supply voltage of 150mV. Low power dissipation is important in some low power applications and lowering supply voltage is the most effective way of decreasing power consumption. This comes at the cost of performance.

#### REFERENCES

- Jyoti Saraswat, Neha Rathi, Partha Pratim Bhattacharya, "Techniques to Enhance Lifetime of Wireless Sensor Networks: A Survey", Global Journal of Computer Science and Technology (E), Volume 12, Issue 14, Version 1.0, September 2012, pp. 1-18.

- [2] Uday B. Desai, B.N. Jai and S.N. Merchant, "Wireless Sensor Networks: Technology Roadmap", A Project supported by Department of Information Technology, Ministry of Information and Communication Technology, India.

- [3] Amit Sinha, Anantha Chandrakasan, Massachusetts Institute of Technology, "Dynamic Power Management in Wireless Sensor Networks", IEEE Design & Test of Computers, March–April 2001, pp. 62-74.

- [4] Neetu Kumari, Nikita Patel, Satyajit Anand, Partha Pratim Bhattacharya, "Designing Low Power Wireless Sensor Networks: A Brief Survey", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 2, Issue 9, September 2013, pp. 4447-4456.

- [5] Xue, S., Oelmann, "Comparative study of low-voltage performance of standard-cell flip-flops", Proc. of IEEE ICECS 2001 2 (2001) 953–957

- [6] Weste, N.H.E., Harris D., "CMOS VLSI Design A Circuits and Systems Perspective", Addison-Wesley, Boston, MA (2005)

- H. P. Alstad and S. Aunet, "Seven subthreshold flip-flops cells," in Proc.IEEE NorCHIP 2007, Nov. 2007, pp. 1-4.

- [8] H. P. Alstad and S. Aunet, "Three Subthreshold Flip-Flop Cells Characterized in 90 nm and 65 nm CMOS Technology", Design and Diagnostics of Electronic Circuits and Systems, 2008. 11th IEEE Workshop, pp. 1-4.

- [9] Wei Jin, Sheng Lu, Weifeng He, Zhigang Mao, "Robust Design of Sub-threshold Flip-Flop Cells for Wireless Sensor Network", 2011, IEEE/IFIP 19th International Conference on VLSI and System-on-Chip, pp. 440-443.

- [10]. Rajesh Kumar Tiwari & G. Sahoo (2011) A Novel Methodology for Data Hiding in PDF Files, Information Security Journal: A Global Perspective, 20:1, 45 -57, DOI: 10.1080/19393555.2010.544703.

- [11] Santosh Kumar Singh, P.K.Manjhi and R.K.Tiwari "Cloud Computing Security and Trust Enhancement by using OTP", International Journal of Innovative Research in Computer and Communication Engineering, (IJIRCCE), Vol.4, Issues5, ISSN: 2320-9798, DOI:10.15680/IJIRCCE.2016.0405069, May 2016.

- [12] R. K. Tiwari and G. Sahoo, "Designing some Imperceptible Data Hiding Methodologies Using Steganographic Techniques", International Journal of Information Technology & Knowledge Management. IJITKM Vol.-I, No-2, Dec. 2008, pp- 209- 217.

- [13] Anoop Joyti Sahoo, and Rajesh Kumar Tiwari "A Novel Approach for Hiding Secret data in Program Files" International Journal of Information and Computer Security. Volume 8 Issue 1, March 2016,

- [14] Abu Salim, Sachin Tripathi and Rajesh Kumar Tiwari "A secure and timestamp-based communication scheme for cloud environment" Published in International Journal of Electronic Security and Digital Forensics, Volume 6, Issue 4, 319-332.

- [15] Rajesh Kumar Tiwari and G. Sahoo, "A Novel Watermark Scheme for Secure Relational Databases" Information Security Journal: A Global Perspective, Volume 22, Issue 3, July 2013.